# The missing Samsung EVO 840 - 250 GB SSD Repair Manual

First version: July 2016 Current version: 2.12.2024

#### Introduction

Unfortunately my Novena laptop got physically damaged, so I took the SSD (Solid-State-Disk) from the Novena to a data-recovery company, who analyzed the SSD and discovered that the SSD has a problem in its startup phase that is most likely due to a firmware corruption, but the physical damage is actually not a problem for the SSD.

According to the company it is very likely that all other Novena SSDs (in Laptops, Desktops and Heirlooms) with the same firmware have the same problem and might also loose data. Therefore I started to work on analyzing the firmware, and the firmware update process.

I have created the following guideline how you can extract and verify the firmware from your SSD, so that we can find out together, which models are actually affected.

I will try to explain what you can do to protect your own SSD, or recover if the same or a similar problem happens to your SSD.

What you should do now:

\* **Backup your data!** But not to a SSD. SSDs seem not to be very well suited for backups from my point of view, I would suggest to use HDDs (Hard-Disk-Drive) instead.

What you should do when such a problem happens to your SSD:

Check back here, perhaps we have a solution for it already.

If you need urgent access to your data, search for a data recovery company that has a PC-3000 SSD from AceLabs available, at the moment of this writing, I think it is likely that they could recover your data with it.

This is how the problem of my SSD looks like from the kernel point of view (the following is the output from the "dmesg" command under Linux):

```

[ 1.203395] ahci-imx 2200000.sata: fsl,transmit-level-mV value 1025, using

00000024

[ 1.203432] ahci-imx 2200000.sata: fsl,transmit-boost-mdB value 0, using

00000000

[ 1.203464] ahci-imx 2200000.sata: fsl,transmit-atten-16ths value 8, using

00002800

```

1.203494] ahci-imx 2200000.sata: fsl,receive-eq-mdB not specified, using Γ 05000000 1.203543] ahci-imx 2200000.sata: Looking up target-supply from device tree Γ 1.206436] ahci-imx 2200000.sata: SSS flag set, parallel bus scan disabled Γ 1.206494] ahci-imx 2200000.sata: AHCI 0001.0300 32 slots 1 ports 3 Gbps 0x1 Γ impl platform mode 1.206531] ahci-imx 2200000.sata: flags: ncq sntf stag pm led clo only pmp Γ pio slum part ccc apst 1.208050] scsi host0: ahci platform Γ 1.208473] ata1: SATA max UDMA/133 mmio [mem 0x02200000-0x02203fff] port Γ 0x100 irg 71 [...] 6.592593] ata1: link is slow to respond, please be patient (ready=0) ſ 11.212587] ata1: COMRESET failed (errno=-16) ſ 16.602585] ata1: link is slow to respond, please be patient (ready=0) ſ 21.222578] ata1: COMRESET failed (errno=-16) [ [ 26.612582] ata1: link is slow to respond, please be patient (ready=0) [ 56.252588] ata1: COMRESET failed (errno=-16) 56.261143] ata1: limiting SATA link speed to 1.5 Gbps Γ 61.292587] ata1: COMRESET failed (errno=-16) Γ 61.301345] atal: reset failed, giving up Γ 61.310158] ahci-imx 2200000.sata: no device found, disabling link. Γ 61.319008] ahci-imx 2200000.sata: pass ahci imx..hotplug=1 to enable hotplug Γ

So it seems the SATA (Serial AT Attachment) host tries to initiate the communication with COMRESET (somewhere between second 1.206531 and second 1.208473), but it never receives the COMINIT answer the SSD should give. 5 seconds later at second 6.592593 is complains that there is still no answer and a minute later at second 61.301345 it gives up. Theoretically the COMINIT should come within a second after the COMRESET.

If you are interested in the details of the SATA protocol, I can recommend this presentation: <u>http://de.slideshare.net/niravdesai7121/sata-protocol</u>

On page 30 you can see the timing of COMRESET and COMINIT. The SATA host (computer) should start with COMRESET, and the SSD should reply with COMINIT. Afterwards they can calibrate, negotiate the speed, ... and then they have a "link".

From OCZ SSDs I have heard that they have some kind of panic lock, where the SSD stops booting to prevent further damage when it discovered a potential problem. This behaviour on OCZ SSDs is often triggered when waking up a Laptop from hibernation. It could be that this is an instance of a similar panic lock for Samsung SSDs.

## Layer 0 - Physical layer

Ok, let's start with the physics.

The SSD is contained in a metal case, to open it you have to open 3 screws, one of them is visible, the other 2 are behind the plastic sticker.

The screw has a Pentalobe format, so you need a Pentalobe screwdriver. I found a working one in the <u>https://www.ifixit.com/Store/Tools/64-Bit-Driver-Kit/IF145-299-1</u>

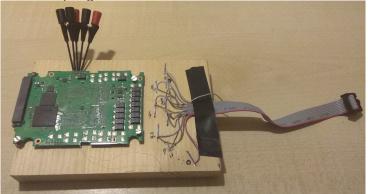

(It's a bit funny that you need a 64 Bit Driver kit to access a 32 Bit CPU ;-) When you have opened it, the SSD PCB (Printed-Circuit-Board) should look like *I* the one on the upper right hand side of this image:

Image 1: Pentalobe

So what do we have here? The long thing on the upper end is the SATA connector, the big square chip on the bottom left is the controller CPU, in the middle we have some SDRAM and on the right side is the actual NAND Flash storage chip.

On the back side is the second NAND Flash chip in the same location (I guess that makes it easy to route the traces, perhaps the address lanes are shared) Another thing that strongly suggests to put 2 NAND Flash chips on directly opposite

sides of a PCB is the temperature sensing. You want a connection that is as short as possible from the temperature sensor to the NAND flash chips where the temperature has to be measured. The easiest way to achieve that is by placing the NAND flash chips at the same location, and the temperature sensor directly next to both of them. (The temperature connection is done by the ground plane in the PCB or a very wide trace)

The controller CPU (the one one the left side of the image) is called Samsung MEX (the product number is S4LN045X01-8030), it has 3 ARM Cortex R4 cores, which are based on the ARMv7-R architecture, and likely have about 400 MHz. MEX is the fifth generation of the chip, MAX was the first one, MBX the second one, ...

The following things are written on the controller CPU: SAMSUNG S4LN045X01-8030 N7Y89MMB U1441 ARM → 1441 means it was produced in the year 2014/Week 41 It is said to have an 8 channel controller, if you want to learn more about what that means, I suggest the following page: <u>http://www.cactus-tech.com/en/resources/blog/details/solid-state-drive-primer-8-controller-</u> architecture-channels-and-banks

The SDRAM chip: Samsung 512 MB Low Power DDR2 SDRAM Samsung, 4Gb, LPDDR2 SDRAM, 1CH x 32, 8 banks, 134-FBGA, MONO, 1066Mbps, 1.8V/1.2V/1.2V: 512MB LPDDR2 DRAM: The following things are written on it: SAMSUNG 440 K4P4G324EQ-FGC2 K:=Memory 4:=DRAM P:=LPDDR2 (guess) 4G:=4G, 8K/64ms Density 32:=x32 Bit Organisation

```

4:=8 internal Banks

E:=Interface ?

Q:=SSTL-2 1.8V VDD, 1.8V VDDQ

-F:=7th Generation

G:=FBGA Package

C:=Commercial, Normal Temperature&Power range (0-

95°C)

```

EXH382HCC

```

And now the NAND chips that actually hold your data:

NAND TLC 128 GB: (19nm Toggle Mode 2.0 TLC (3-bit per cell) NAND (Model#

K90KGY8S7M-CCK0))

SAMSUNG 440

K90KGY8S7M-CCK0

K:=Memory

9:=NAND Flash

0:=3-Bit MLC (TLC)

KG=128G

Y8=Organisation x8?

S=Voltage ?

7=Mode ?

\mathbf{M}=1st Generation

C=CHIP BIZ D : 63-TBGA

C=Commercial, Normal(0°C-95°C) & Normal Power

K=Customer Bad Block ?

0=Pre-Program Version:None

```

I measured the voltages and connectivity of a very similar PCB which uses the same Controller and slightly different Flash chips to create a pinout: <u>http://www2.futureware.at/~philipp/ssd/K9CHGY8S5M-CCK0-Pinout.pdf</u> The chip has 0.8mm pitch and BGA-316 form factor.

#### K9CHGY8S5M-CCK0 Pinout

|    | SAIVIS | SONG | KaCU | 6103                                    | SIVI-CO |      | mout |      |      |      |      |      |      |      |      |    |    |

|----|--------|------|------|-----------------------------------------|---------|------|------|------|------|------|------|------|------|------|------|----|----|

|    | 1      | 2    | 3    | 4                                       | 5       | 6    | 7    | 8    | 9    | 10   | 11   | 12   | 13   | 14   | 15   | 16 | 6  |

| Α  |        |      |      |                                         |         |      |      |      |      |      |      |      |      |      |      |    | Α  |

| В  |        |      |      | 1,84                                    | GND     | 1,83 | GND  | 0,91 | 2,95 | GND  | 2,95 | GND  | 2,95 |      |      |    | в  |

| С  |        |      | GND  | 2,96                                    | GND     |      | 0,9  |      |      | 1,84 | GND  |      |      | 12,3 |      |    | С  |

| D  |        | 2,96 | GND  |                                         |         |      | 0,9  |      |      | GND  | GND  | GND  | GND  | GND  | 2,96 |    | D  |

| Е  |        | 1,83 | GND  |                                         |         | 0,59 | 0,9  |      |      | GND  | 1,83 |      | GND  | GND  |      |    | E  |

| F  |        | GND  | GND  | 1,83                                    | GND     | 0,58 | 0,89 |      |      |      | 1,83 |      | GND  | GND  | GND  |    | F  |

| G  |        | 1,83 | GND  | 2,96                                    | GND     |      |      |      |      | 1,84 | 1,83 | 1,83 |      | GND  | 2,96 |    | G  |

| н  |        | 2,96 | GND  | 1,83                                    | GND     | 1,83 | 1,82 |      |      |      |      | 1,83 |      | GND  |      |    | н  |

| J  |        | 1,83 | 1,84 | GND                                     | 0,58    | 0,57 | 1,83 |      |      |      |      | 1,84 | 0,2  | GND  | GND  |    | J  |

| к  |        | 1,83 | GND  | GND                                     | 0,57    | 0,59 | 1,83 |      |      | 1,83 |      | 1,84 |      | GND  | 2,95 |    | к  |

| L  |        |      | GND  |                                         | 0,6     | 0,59 | 1,83 |      |      | 1,83 | 0,89 | 0,97 |      | GND  | 1,83 |    | L  |

| М  |        | 1,84 | GND  |                                         | 0,59    | 0,59 | 1,83 |      |      | 1,83 | 0,9  | 0,97 |      | 0,91 |      |    | м  |

| Ν  |        | 2,96 | GND  |                                         | 1,83    |      |      |      |      | 1,83 | 0,91 | 0,95 | GND  | GND  | 1,84 |    | N  |

| Р  |        | GND  | GND  |                                         | 1,83    |      |      |      |      |      | 0,91 | 0,94 | GND  | 1,82 | 1,84 |    | Р  |

| R  |        | 2,95 | GND  |                                         | 1,83    |      |      |      |      | 1,82 | 1,82 | GND  | 1,84 | GND  | 2,96 |    | R  |

| т  |        | 2,96 | GND  |                                         | 1,83    | 1,83 | 1,84 |      |      |      |      | GND  | 2,96 | GND  | 1,84 |    | Т  |

| U  |        |      |      | GND                                     |         | 1,84 | GND  |      |      | 0,87 | 0,87 | GND  | 1,84 | GND  | GND  |    | υ  |

| v  |        |      | GND  | GND                                     |         | 1,83 | GND  |      |      | 0,87 | 0,9  | 0,2  |      | GND  | 1,83 |    | v  |

| w  |        | 2,95 | GND  | GND                                     | GND     | -    | GND  |      |      | 0,87 | 0,89 |      |      | GND  | 2,96 |    | w  |

| Y  |        |      | 12,3 |                                         |         | GND  | 1,83 |      |      | 0,88 | 0,87 | GND  | -    | GND  |      |    | Y  |

| AA |        |      |      | 2,95                                    | GND     |      | GND  | 2,96 | 0,91 | GND  |      | GND  | 1,84 |      |      |    | AA |

| AB |        |      |      | , , , , , , , , , , , , , , , , , , , , |         |      |      |      |      |      |      |      |      |      |      |    | AB |

|    | 1      | 2    | 3    | 4                                       | 5       | 6    | 7    | 8    | 9    | 10   | 11   | 12   | 13   | 14   | 15   | 16 |    |

|    | _      | _    | _    | -                                       | _       | -    | -    | _    | -    |      |      |      |      |      |      |    |    |

#### SAMSUNG K9CHGY8S5M-CCK0 Pinout

Yellow: this pin is connected to the same pin of another flash chip e.g. Power-Lines are usually connected the same way (yellow) e.g. Chip-Select lines are connected differently (gray) 1,83-1,84 Volt power rail, all connected together on the PCB 2,96 Volt Power-Rail, all connected together on the PCB

12 Volt Power-Rail, all connected together on the PCB 🚽

Form-Factor: BGA-316, 16 CE\_n assignments for quad 8-bit data access Pin Reduction does not seem to be used

The only product selection guide that contained relevant information that I could find was from 2010, so it did not contained all variations, but it is still a helpful guide to understand Samsung's naming conventions:

http://www.samsung.com/global/business/semiconductor/file/media/SamsungPSG\_july2010\_final-2.pdf - Page 16

If anyone can provide any further information to explain the variations we have here, I would be interested to hear.

Unfortunately at first I couldn't find datasheets for any of the other chips used on the SSD.

There are a few smaller chips on the PCB: JS4TAA and AKE4QD, "ABS 431 .WD" There is also a Chip named "GUILL TI 48" on it, which is from Texas Instruments <u>https://chipworks1.force.com/DefaultStore/ccrz\_ProductDetails?</u> <u>viewState=DetailView&cartID=&sku=TEX-GUILL\_PKG\_2&store=DefaultStore</u>

fzabkar from forum.hddguru.com has identified the chips and provided the following information:

"The mystery components appear to be marked especially for Samsung.

JS4TAA appears to be a SY20855A which is a "6.5V 5A Current Limit Switch with OVP Clamp" electronic fuse manufactured by Silergy. "JS" appear to be the important characters in the part number. The datasheet is available here:

https://www.mouser.com/datasheet/2/850/SY20855A\_6\_5V\_Input\_5A\_Current\_Limit\_ Switch\_with\_O-3435652.pdf

GUILL is a TPS62130D2 synchronous step-down DC-DC converter manufactured by Texas Instruments.

AKE40D appears to be a multiple-output switchmode DC-DC converter, probably with integrated power sequencing. "AKE" appear to be the important characters in the part number.

I'm guessing that the ABS part is an SPI flash memory."

The ABS part is actually not a SPI flash, but a I2C device, and my current guess is that it is the temperature sensor, similar to those devices:

http://www.ti.com/lit/ds/symlink/tmp275.pdf

http://www.nxp.com/documents/data\_sheet/LM75A.pdf

http://ww1.microchip.com/downloads/en/DeviceDoc/25095A.pdf

I logged the following I2C communication with an Oscilloscope: I2C

Time, Dir, ID, Data, ACKed,

1.0870288E-01, Write, 18, 08 02, Y,

1.0890320E-01,Write,18,00,Y,

1.0903376E-01,Read,18,00 77,N,

1.0923408E-01,Write,18,01 02 29,Y,

1.0949680E-01, Write, 18, 04 05 50, Y,

1.0975952E-01,Write,18,04,Y,

1.0989008E-01,Read,18,05 50,N,

1.1008976E-01,Write,18,02 05 00,Y,

1.1035280E-01,Write,18,02,Y,

1.1048336E-01,Read,18,05 00,N,

1.1068304E-01, Write, 18, 03 04 B0, Y,

1.1094608E-01,Write,18,03,Y,

1.1107664E-01,Read,18,04 B0,N,

On (another?) SSD I got the following I2C traffic for every Smart command:

Write 0x30 Data 05h

Read 0x31 Data 22h 2Ch

So 0x05 is obviously the command to read out a single temperature value, and for the temperature values we read, we got the following table:

22 A8 = 42°C 22 88 = 40°C 22 48 = 36°C 22 3C = 35°C 22 38 = 35°C 22 34 = 35°C 22 2C = 34°C 22 20 = 34°C

$1C = 33^{\circ}C$  $1C = 33^{\circ}C$  $18 = 33^{\circ}C$ With the 2 constants 0x30 followed by 0x31 I was able to identify the I2C code in the firmware.

On the various SSDs from Samsung the ABS part, or a similar chip is always located directly besides the Flash chips on the PCB, which is necessary to measure the temperature. (You could put a SPI flash anywhere on the board)

I found the following document which explains the thermal management strategy of Samsung with their newer 950 series starting at page 13:

http://www.samsung.com/semiconductor/minisite/ssd/downloads/document/ Samsung SSD 950 PRO White paper.pdf

So the thermal management that is used in the EVO840 is likely similar but not that advanced.

Later on the actual "ABS" chip was found by fzabkar: MCP9844T-BE/MNY, Microchip, +/-1 degC, 1.8V Digital Temperature Sensor, marking ABS, TDFN-8:

http://ww1.microchip.com/downloads/en/DeviceDoc/20005192B.pdf

### Layer 1 - Link layer

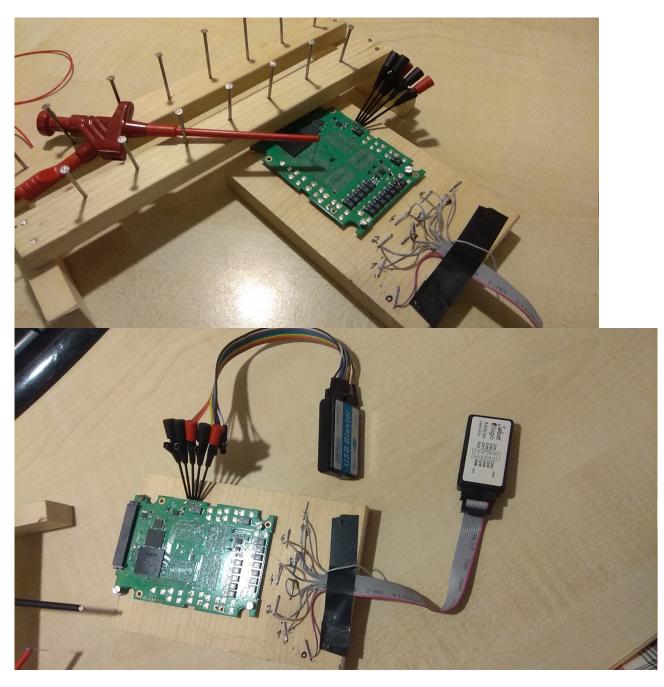

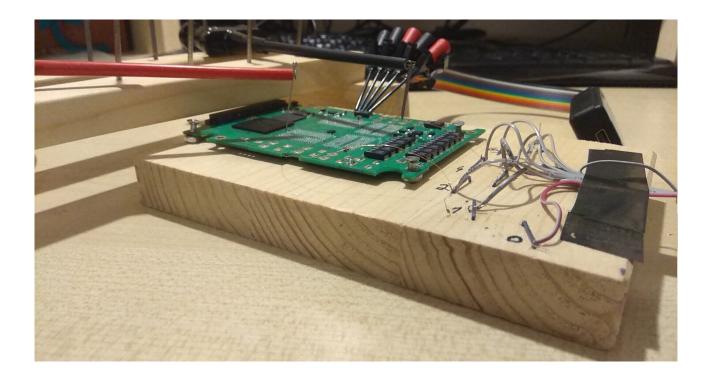

SSD's need to be electrically powered, this one needs to be powered through the SATA port. At first I used a USB-SATA adapter for supplying power.

One relevant topic regarding the power-supply is the grounding for the JTAG port: I tried to attach the USB-SATA adapter to the USB power of a secondary laptop, and there I measured a nearly constant 2 Volt difference between the GND (ground) of the SSD and the GND of the Novena.

The signal level of the GPIOs of Novena is 3.3 Volts, so I thought that +- 2 Volts could be too much for proper signaling reception.

When I plugged the USB adapter into a USB port of the Novena, both Novena and SSD had the same GND level (0 Volt difference).

The downside of the USB-SATA adapters is that you do not get access to the initialization communication so PCI SATA adapter or SoC is preferred if you want to analyze the SATA behavior.

I powered the SSD and measured all the voltages on all the Pins I could find, first on a good SSD, documented on printed up-scaled photos and then verified them on my broken SSD, and the voltages were all OK.

The voltages on the SATA Data pins were identical too, so I have some more confidence that the problem is not a physical problem of the SATA interface, and that all the power-management is good.

You can measure the power with a multi-meter on various places. Make sure that you configure your multi-meter correctly to read voltages, and that you always touch only a single pin, that you do not short out 2 pins next to each other. When you have sharp probe heads, make sure you do not push too hard on the pins, to not squish the pins!

I have created a separate PDF with both front-side and backside images where you should be able to better zoom in so that you can look at the details: http://www2.futureware.at/~philipp/ssd/SamsungEVO840Voltages.pdf

Later on I took an Arduino with a 4-Relais shield and connected 2 power cables to it, so that I can switch on/off the SATA power supply (one relais for the 5V rail and one relais for the 12V rail, and finally one relais for the Safe-Mode) programmatically by sending switch on/off commands to the Arduino. Nowadays I would recommend a dedicated USB relais board with at least 4 ports, I don't like the connection between the Arduino and the relais board, it isn't very stable.

Controlling the SATA data port was done later on by using a USB-SATA converter connected to the USB port on the Novena, which can be controlled with the novena-usb-hub tool. (It enables/disables the power supply to the USB port)

# JTAG

Now regarding the JTAG interface: I found the JTAG pinout of the Samsung SSD on Twitter: https://twitter.com/bsmtiam/status/623241828033114112

(Thanks a lot to bsmtiam!)

I found some more pins on the board:

There are 2 pins right next to the JTAG interface (which I marked 0V, 1.8V TRST on the second photo). The one next to the JTAG pins is a RESET line (TRST/RESET).

Later on I found that ACE Laboratory (makers of PC-3000) figured out the 4 pins next to JTAG: The 2 pins right next to the JTAG (0V, 1.8V) pins are activating the "SAFE Mode" when shorted. The other 2 pins (marked 1,815 V and 1,819V) are a UART port, which provides debugging functionality in SAFE Mode.

The big round connectors are GND.

On the other side, next to the CPU (big quadratic chip), there are 6 Test\_Pins which I number the following way:

Pin#1 would be the one nearest to the SATA connector, PIN#6 is the one farthest away from the SATA connector.

Pin#1 is connected to a pin of an unpopulated footprint nearby. Pin#1 has 1.816V voltage (and 7MegaOhm to GND), the same is on the connected pad of the unpopulated footprint nearby. The other pad of the unpopulated footprint has 0V voltage and is connected with GND. (So the unpopulated footprint is likely for a Pull-Down Resistor or a Capacitor)

Pin#5 is connected to the "Optional" pin on the SATA power connector. This is likely a GPIO from the CPU. See <u>http://www.samsung.com/semiconductor/minisite/ssd/downloads/document/</u><u>Samsung\_SSD\_845DC\_01\_Device\_Activity\_Signal\_DAS.pdf</u>

Now where to get a JTAG adapter?

Well, the Novena has a few GPIOs that are pinmuxed (multiplexed) with the serial ports and are easily accessible:

https://www.kosagi.com/w/index.php?title=Novena\_headers\_to\_linux\_GPIO\_mappings

I wanted to use the Novena as a JTAG master without a SATA disk, so that I could plug the diskunder-test into the SATA port if I wanted too, so I took a spare 4GB MicroSD card and installed the standard Novena image on it: <u>http://repo.novena.io/novena/images/novena-mmc-disk-r1.img</u> I learnt about the pinmuxing in Linux called PINCTRL

(<u>https://www.kernel.org/doc/Documentation/pinctrl.txt</u>), and learnt that it is defined in the device-tree.

I tried out the pins, and found that only 2 of the documented pins were actually usable as GPIOs, the other pins were not configured in the device-tree.

So I tried to update the kernel from the repository ( <u>https://www.kosagi.com/w/index.php?</u>

<u>title=Updating novena repo key</u> ) to the current 4.4 kernel, which also came with a new devicetree configuration, and suddenly I could drive 4 of the pins as GPIOs, which is sufficient for basic JTAG access.

If you have a Samsung 840 EVO but you do not have a Novena board, you can also use/buy a cheap Altera USB Blaster which is about 3 times slower than the Novena with sysfsgpio.

I also bought various other JTAG interfaces which did not work: In-Circuit Open-OCD, BAITE JTAG ICE, Raspberry Pi 3, OLIMEX ARM-USB-OCD-H all did not work. The Raspberry Pi3 showed signal integrity issues that might possibly be overcome with an improved driver.

So for the Novena, you need the following OpenOCD configuration: interface sysfsgpio transport select jtag # Each of the JTAG lines need a gpio number set: tck tms tdi tdo sysfsgpio\_jtag\_nums 163 16 162 20

Then I wanted to try the RESET line, so I needed 1 or 2 more GPIOs. I changed the Device-Tree to pinmux the lines from UART to GPIO, and documented everything on the Wiki: <a href="https://www.kosagi.com/w/index.php?title=Novena">https://www.kosagi.com/w/index.php?title=Novena</a> as JTAG adapter

One problem I found out later on is that Novena and Raspberry Pi GPIOs are somewhat slow, and that you might want to try faster JTAG adapters. With my Novena and OpenOCD I was able to read memory with 6 Kbyte/second. With the newer imx\_gpio driver, it is raised to 8 Kbyte/second. I added a toggle command into OpenOCD and improved it to 13KB/s. The bottleneck with sysfsgpio is the Linux Kernel API for GPIOs, where you need 2 syscalls per toggle. Creating a faster Kernel interface and perhaps DMA accelerating the GPIOs should speed it up a lot. If anyone could implement that in the Linux kernel and in OpenOCD, that would be great.

Later on I bought and tried several other JTAG interfaces, but I had a lot of troubles with them, the Samsung SSDs seem to be very picky about signal integrity and voltages (1.8V!!!). So far, Novena and Altera USB Blaster (the normal ones, a Revision C marked one did not work for me) are still the only reliable JTAG adapters for Samsung SSDs.

## Safe Mode

I found a product called PC-3000 on the market for data recovery that is able to recover data from Samsung SSD's: <u>http://www.acelaboratory.com/pc3000-SSD.php</u> through the SATA interface.

When you click on "Video Tutorials" and watch the Samsung video, it shows that you have to shorten 2 pins on the PCB and then power on the SSD to get the SSD into "Safe Mode". Several weeks later I found a better video:

http://blog.acelaboratory.com/pc-3000-ssd-samsung-family.html

The RESET line has to be shorted to the pin next to it during powerup, and afterwards there is a UART available on the other 2 pins.

From what I have read, back in the HDD world, Safe-Mode meant that the harddisk would not power up the motors to actually read/write on the harddisk, so you could safely talk to the HDD controller chip about it's firmware, without risking any power problems.

It was not quite clear for me, what Safe-Mode could actually mean for a SSD.

After some playing around with SAFE-Mode, I found out it means the following:

\* Only the first Core mex1 is activated, mex2 and mex3 are unpowered in SAFE-Mode, which hints that in normal (non-SAFE) mode, mex1 is responsible for waking up mex2 and mex3 likely somewhere at the end of the initialisation.

\* The SSD claims to have about 500 MB size, not 250 GB anymore, which resembles the RAM size in the SSD, so you most likely get direct access to the RAM this way (which is where the is read from/to on the way to the Flash). Reading anything didn't gave me any of the original contents, so it also seems as if the Flash isn't mounted, the Flash encryption is not active, ...

\* It always has the serial number SN00000000000, so it obviously tries not to read anything from the configuration that is stored in the Flash, so that it cannot crash during the initialisation due to garbage in the configuration memory.

On the ARM side of things, I found that there is a Processor PIN called VINITHI that is read(sampled) once during boot, which decides, whether the CPU should boot from the address 0x00000000 or from the address 0xFFFF0000. So theoretically this ARM Pin could be the Safe Mode pin, so that it boots from a different code there. But I did not see any memory available at 0xFFFF0000 during any of my traces, so this option seems to be unlikely. It could be that there is some memory mapped at 0xFFFF0000 during boot and unmapped again by the boot code, but I did not saw any hints about that yet, so I think that is not the method used for booting. So if the Safe-Mode exists (yes, it does) on EVO 840 – 250 GB, and it is not the Processor Pin to run at 0xFFFF0000, then I think it would have to be a GPIO and the firmware would have to branch depending on the GPIO afterwards, which would be read by the Firmware during booting. It finally turned out that the Safe-Mode pin is actually just one of many GPIO pins (UART, I2C), which is sampled by the first stage bootloader.

From the physical point of view: Since there are no >3 Volt Test-Pins available anywhere on the board, the connection between the 2 pins would likely have to pull the GPIO down to GND. To be able to measure a grounded Pin and to differentiate it from a free floating pin, a voltage has to be applied, something like 1.8 V would be what I would expect there.

If this voltage is only applied during booting, then an oscilloscope with triggering is needed to analyze it.

#### Layer 2 - Firmware

At first I searched on the Internet for Firmware updates.

On the Samsung website there is only the current firmware update available. But searching on the internet some more, I was also able to find previous firmware updates.

This is the current Firmware history I compiled:

1: EXT0AB0Q (~2013-07) (Original firmware, I could not find it on the internet)

2: EXT0BB0Q (2013-10)

3: EXT0BB6Q (2013-12-18 19:43) (currently available on the Samsung website)

4: EXT0CB6Q (2014-10-10 19:36) This is included in the

Samsung\_SSD840EVO\_Performance\_Restoration.zip

5: EXTODB6Q (2015-03-27 18:35)

When you download the ISO image to update the firmware you get a file like this: Samsung\_SSD\_840\_EVO\_EXT0BB6Q.iso

Inside the file there is the isolinux/btdsk.img , which can be unpacked with 7-Zip.

Inside the btdsk.img there are 3 interesting files:

samsung/DSRD/DSRDGUI0.EXE (firmware updater)

This EXE file is packed with WDOSX and can be unpacked with WDOSXUnpacker (which requires Python 2.7, it does not run unter Python3!):

https://raw.githubusercontent.com/0xDB/WDOSXUnpacker/master/WDOSXUnpacker.py

Then you have 2 files for the firmware:

samsung/DSRD/DSRD.enc (firmware update configuration file)

samsung/DSRD/FW/ext0bb6q/EXT0BB6Q.enc (firmware itself)

I decrypted half of it, which allowed me then to find a tool that is able to fully decrypt them: <u>https://github.com/ddcc/drive\_firmware/blob/master/samsung/samsung.c</u> The obfuscation is a 4-Bit encryption of the upper nibbles in every byte. I hope that this ishei not the only protection mechanism against malicious firmware-updates.

The firmware update configuration file contains a list of old firmware versions it can be applied to, and which new firmware version they should get, and I think whether a restart is needed.

At first I tried to decompile the firmware, but I saw that there are several problems with this approach: ARM has a Thumb mode, which is a different ISA (Instruction Set Architecture) that is only 16 bits per command, and it can switch between ARM (32 Bit) and THUMB (16 Bit) mode back and forth with every jump/call. So it depends on the compiler what code it wants to generate, and it is hard to guess whether a particular DWord is actually 1 ARM instruction or 2 THUMB instructions just from the raw binary. The usual method is to take one known entry point (assuming that the CPU normally starts in ARM mode, not in Thumb mode), and then follow to any jump/calls and learn from them whether the targets points are actually ARM or Thumb. But since I did not knew any entry points in the beginning, that approach did not looked good to me. The approach I decided to do is to single-step debug through the firmware through the JTAG interface, and to record for every single-stepped instruction, whether it is ARM or Thumb and then to feed those information from the traces back into the disassemblers and decompilers, which memory areas contain ARM code or Thumb code. (Look for .r2 files that are generated). Another problem is the memory mapping. The firmware file consists of 10 parts that are loaded to different memory regions, and later on I found out that some of them are additionally mapped to other ranges, and that partly depends on the actual CPU core they are running on. This actual mapping is also interesting and helpful for disassembling/decompiling it.

Then I analyzed the format of the firmware file, and found that it contains a header, then 10 partitions (nicely aligned and not overlapping), and at the end some data that is outside the partitions. The previous firmware versions had a very similar structure, only a few partitions had slightly different sizes.

http://www2.futureware.at/~philipp/ssd/analyse/EXT0CB6Q.dec.html

# Layer 3 - Communication

After succeeding to setup the JTAG link, I started OpenOCD and configured it. I created the following configuration files:

novena-jtag.tcl Novena JTAG configuration

<u>novena-swd.tcl</u> Novena SWD configuration (this is not applicable to this SSD, but if you want to analyze some other board which has a SWD interface with your Novena, this file is what you need. <u>samsung-mex.tcl</u> Samsung MEX configuration

You then run OpenOCD with both configuration files:

openocd -f novena-jtag.tcl -f samsung-mex.tcl

I have copied both files into a openocd.cfg so that I can start openocd with "openocd -f openocd.cfg"

(If you are using a raspberry instead of the Novena, you would use some configuration for raspberry together with the samsung-mex.tcl instead of the novena-jtag)

### **JTAG SCAN:**

Instructions 0-7 all seem to be only one Bit long, which is always zero. But it could also be 0 bits long. FFFFFFFFFFFFFFF > irscan auto0.tap 0 ; drscan auto0.tap 64 0x0 FFFFFFFFFFFFFFF > irscan auto0.tap 1 ; drscan auto0.tap 64 0x0 FFFFFFFFFFFFFFF > irscan auto0.tap 2 ; drscan auto0.tap 64 0x0 00000000000000000 FFFFFFFFFFFFFFF > irscan auto0.tap 3 ; drscan auto0.tap 64 0x0 > irscan auto0.tap 4 ; drscan auto0.tap 64 0xfffffffffffffffff FFFFFFFFFFFFFFF > irscan auto0.tap 4 ; drscan auto0.tap 64 0x0 0000000000000000 FFFFFFFFFFFFFFF > irscan auto0.tap 5 ; drscan auto0.tap 64 0x0 00000000000000000 > irscan auto0.tap 6 ; drscan auto0.tap 64 0xffffffffffffffff FFFFFFFFFFFFFFF > irscan auto0.tap 6 ; drscan auto0.tap 64 0x0 0000000000000000 FFFFFFFFFFFFFFF > irscan auto0.tap 7 ; drscan auto0.tap 64 0x0 00000000000000000 Now it gets interesting starting from instruction 8 (0100): Here we have a 32/37 Bit register. This is called the JTAG DP ABORT according to the specs. > irscan auto0.tap 8 ; drscan auto0.tap 64 0xffffffffffffffff FFFFFF80000000 > irscan auto0.tap 8 ; drscan auto0.tap 64 0x0

####

Instructions 10 and 11 have some strange set/reset logic in them: > irscan auto0.tap 0xb ; drscan auto0.tap 64 0x000000000000 00000000000009A > irscan auto0.tap 0xb ; drscan auto0.tap 64 0x000000000000 00000000000009A > irscan auto0.tap 0xb ; drscan auto0.tap 64 0x000000000000 00000000000009A > irscan auto0.tap 0xb ; drscan auto0.tap 64 0x000000000000 00000000000009A > irscan auto0.tap 0xa ; drscan auto0.tap 64 0xfffffffffffffffff FFFFFF8000009A FFFFFF80000002 > irscan auto0.tap 0xa ; drscan auto0.tap 64 0xffffffffffffffff FFFFFF80000002 > irscan auto0.tap 0xa ; drscan auto0.tap 64 0x0 000000000000002 > irscan auto0.tap 0xa ; drscan auto0.tap 64 0x0 0000000000000002 > irscan auto0.tap 0xa ; drscan auto0.tap 64 0x0 0000000000000002 > irscan auto0.tap 0xb ; drscan auto0.tap 64 0x000000000000 000000000000002 > irscan auto0.tap 0xb ; drscan auto0.tap 64 0x000000000000 00000000000009A > irscan auto0.tap 0xb ; drscan auto0.tap 64 0x000000000000 00000000000009A

> irscan auto0.tap 0xb ; drscan auto0.tap 64 0xfffffffffff FFFFFF8000009A > irscan auto0.tap 0xb ; drscan auto0.tap 64 0xffffffffffff FFFFFF8000009A > irscan auto0.tap 0xb ; drscan auto0.tap 64 0xfffffffffff FFFFFF8000009A > irscan auto0.tap 0xb ; drscan auto0.tap 64 0x000000000000 000000000000009A > irscan auto0.tap 0xb ; drscan auto0.tap 64 0x000000000000 00000000000009A > irscan auto0.tap 0xb ; drscan auto0.tap 64 0x000000000000 00000000000009A > irscan auto0.tap 0xa ; drscan auto0.tap 64 0xfffffffffff FFFFFF8000009A > irscan auto0.tap 0xa ; drscan auto0.tap 64 0xfffffffffff FFFFFF80000002

And Instruction 15 (which should be BYPASS) seems to be 0:

If I didn't overlooked something, it seems that there is no Boundary-Test support available on the Samsung MEX :-( this would have been helpful to test the various traces on the PCB, whether they might be broken/shorted/...

I was hoping for a EXTEST/SAMPLE support to be able to boundary test the BGA balls, to make sure there is no physical problem there, like cold solder joints, unconnected BGA balls, ...

If anyone from Samsung or other vendors reads this: Please make sure in the future that your chips have Boundary-Scan available and provide at least BSDL files in your repair manual for

professional failure analysis, even if there is only one Boundary scan-able chip on it, and Boundary Scan does not seem to make much sense on first sight.

Later on with the SAFE-Mode, I discovered that the SATA Port physically works properly, so the boundary scan is not necessary for me anymore, but I still believe that it would be helpful for other customers to be able to boundary test the devices in the field, to better diagnose problems.

### Layer 4 - Memory

I bought a similar SSD, which luckily had the same PCB design, same chipsets and even the same Firmware version (EXT0CB6Q).

So I dumped the whole memory (tried through the full 4 GB address space of the 32 Bit processor). I decided to separate the whole memory into 64KByte blocks. (Divide & Conquer)

I tried to read every 64KByte block. If the block was readable, it would take approximately 10 seconds (6 KB/s through JTAG. I would be interested if anyone got better performance with different JTAG adapters).

(Note for future projects: 64 KByte Blocks is perhaps too large, there might be smaller memory blocks somewhere.) In normal mode, I did not discover any smaller blocks, only in SAFE mode, I found a 32 KByte Block, or perhaps it was 96 KByte.

If the block was not readable, it would take approximately 1 second.

In parallel, I developed a single-stepper that traces through the firmware, and logs the Program-Counters and ARM<->Thumb instruction set changes, to get a feeling for where the CPU usually hangs out, and where code-regions are, and which instruction set they are using. The information about the instruction set is important for disassemblers like radare2, which have a hard time to guess the instruction set from raw firmware files otherwise.

The broken SSD continuously cycles through the following locations: 0x0081b814, 0x0081b816, 0x0081b818, 0x0081b81a, 0x0081b824, 0x0081b826, 0x0081b82a

The following is a dump of the register values: (0) r0 (/32): 0x203B0000 (dirty) (1) r1 (/32): 0x00000000 (2) r2 (/32): 0x00008000

```

> mex arm disassemble 0x0081b810 20 thumb

0x0081b810 0x408a

LSLS

r2. r1

0x0081b824

0x0081b812 0xe007

В

0x0081b814 0x68c1

LDR

r1, [r0, #0xc] (Read word from

0x203B0000+0xc=0x203B000C)

UXTH r1, r1

0x0081b816 0xb289

; Clears the upper 16 Bits

0x0081b818 0x4211

TSTr1, r2

; Checks for 0x8000

0x0081b81a 0xd003

BEQ

0x0081b824

; It is usually equal

0x0081b81c 0x68c1

LDR

r1, [r0, #0xc]

0x0081b81e 0xf362010f

BFI r1, r2, #0, #16

0x0081b822 0x60c1

STR

r1, [r0, #0xc]

0x0081b824 0x68c1

LDR

r1, [r0, #0xc] ; so we continue here, Loading the value again

0x0081b826 0xea124f11

TST.W r2, r1, LSR #16 ; Test r2 with r1 shifted left (?)

BEQ

0x0081b82a 0xd0f3

0x0081b814

; Branch if Equal, this is usually equal

0x0081b82c 0x4770

BX r14

0x0081b82e 0x0000

LSLS

r0, r0, #00

0x0081b830 0x0000

r0, r0, #00

LSLS

MOVS r0, #0x38

0x0081b832 0x2038

0x0081b834 0xb570 PUSH

{r4, r5, r6, r14}

0x0081b836 0x4604

MOV

r4, r0

0x0081b838 0x4615

MOV

r5, r2

0x0081b83a 0x0780

LSLS

r0, r0, #0x1e

```

Sometime later, I discovered that the different CPU cores have an at least slightly different view on the memory: > mex1 mdw 0x40825088 0x40825088 44465331 1SFD > mex2 mdw 0x40825088 data abort at 0x40825088, dfsr = 0x000000d embedded:startup.tcl:21: Error: error reading target @ 0x017aa > mex3 mdw 0x40825088 data abort at 0x40825088, dfsr = 0x0000000d embedded:startup.tcl:21: Error: error reading target @ 0x017a4

These differences need further investigation.

The current results intermediate results are the following:

ATCM (A-Tightly-Coupled-Memory), starts at 0x0000000 and is 96-128KB large, this is individual memory per CPU-core. Core-1 gets the ROM with the bootloader instead of the ATCM at 0x00000000 when loading in SAFE-Mode. I haven't figured out how this is implemented, and haven't found a mechanism how this memory mapping could be changed from the CPU. BTCM is loaded at 0x800000 and is 8MB shared between all the CPUs.

Later on, I discovered that the internal SPI flash is most likely 128KB in size, and it contains only the firmware that is used in SAFE mode, it does not contain any keys or the normally used firmware. The normally used firmware is stored in the so called SA area on the big NAND flash chips, most likely directly at the beginning of the NAND flash.

### Layer 6 - Multi-Tasking

To get more information about the SSD, I started to do some behavioral analysis:

- I applied different workloads:

- \* Reading sectors from the SSD

- \* Writing sectors to the SSD

- \* Reading geometry info from the SSD

- \* TRIMing sectors on the SSD

- (\* Firmware update I have not tried that yet)

Those workloads are implemented in the workload\_\*.sh files.

Then I tried to selectively turn off and on the 3 CPU cores of the Samsung SSD through JTAG. For reading and writing, I discovered that all 3 cores are needed.

If I halt any of the cores, the data transfer is stalled and it can only complete (or would timeout eventually) if I resume all 3 cores again.

Then I wanted to find out in which order the cores work together.

So I developed a tool that can try all possible variants of turning on and off the various cores(<u>cores1.pl</u>), and find out which is the shortest path to successfully complete the workload (<u>corestrategy.pl</u>).

When I tried this on a hdparm "geometry info" function (which queries from the SSD information about the size and geometry of the disk), it gave the result that it first needs a timeslice on core mex1 and then a timeslice on mex2, mex3 is not needed.

(And mex1 and mex2 do not need to be on at the same time)

Which brought me to the following theory:

mex1 is responsible for receiving data through SATA

mex3 is responsible for communicating with the NAND Flash, where the actual data is stored mex2 is responsible for replying back through SATA

For reading or writing a sector from the SSD, the following timeslices are needed:  $1 \rightarrow 2 \rightarrow 3$  or  $1 \rightarrow 3 \rightarrow 2$ .

So mex1 must come first (to parse the SATA request), then 2 and 3 must come afterwards, interestingly in any order?!? (This fact leads to the hint that there must be a SATA core, which is independent of the 3 ARM cores, which sends the response as soon as both cores have committed their parts to it.

(You can try those with the corestrategy.pl, which calls cores1.pl)

So all those 3 tasks can be handled (mostly) independently in parallel.

Later on it turned out that the cores have different roles than I thought: mex1 is responsible for taking commands from SATA (and likely also PCIe), it does initial parsing and then delegates to mex2 and mex3 for load balancing. mex2 and mex3 are nearly identical, and each of them controls 4 flash channels, which make 8 flash channels in total. mex2 and mex3 both can finalize a SATA response. Even later I found out that mex1 is likely called "HCORE" which stands for HOST-CORE, the core that interfaces to the host, the computer. And mex2 and mex3 are called FCORE, FLASH-CORE, they are responsible for interfacing with the FLASH. But since that information came too late, I will continue calling them mex1, mex2 and mex3 in this paper.

### Layer 7 - Application

What I am primarily interested is resurrecting the SATA PHY (the physical interface for the SATA interface). But where is it?

So I searched for the SATA PHY.

One problem I learned with the workload testing above is that there are various timeouts in the SATA protocol, so that any request for reading/writing a block should finish within seconds rather than minutes.

Tracing the whole handling of the SATA controller during such a request is too slow.

And when the timeouts are reached, in some situations the computer and the SSD are getting so much out-of-sync that they are not able to recover the communication anymore,

and I have to manually disrupt the SATA communication by unpowering the USB-SATA bridge. (This could be perhaps automated by Novenas USB-Hub powering through GPIOs, I haven't tried that yet)

So I transported the idea of DNA-sequencing into Debugging:

I designed a workflow to continuously read a single sector from the SSD with a distinctive address:

```

while true

do

dd if=/dev/sda of=/dev/null count=1 skip=1251255 #0x1317b7

#dd if=/dev/sda of=/dev/null count=1 skip=4235125 #0x409F75

done

```

While running this workflow, I usually let all the cores run. I randomly interrupt one core, trace and log 30 instructions, then I resume the core, so that it can fulfill the request and still be hard-realtime compliant. Similarly to Gene sequencing, I get short snippets of 30 instructions each, which are randomly overlapping, which can be puzzled together again. (See <u>puzzle.pl</u>) Some benchmarking: 1 Instruction: 3 seconds (mostly overhead), 10 Instructions: 5 seconds, 30 Instructions: 12 seconds, 100 Instructions: 31-44 seconds

One thing that helps a lot there is that I initially decided to log with each instruction what the next instruction after it actually is. So it would even work with single instruction snippets. So I ran the workload and collected snippets, and then I searched through the snippets I got for the distinctive address I used for reading the block, and I found parts of it.

```

0x00000af8->0x00000afa Thumb Supervisor 0x00000af8 0x78c9 LDRB r1, [r1, #0x3]

r1:0x00800D80=>0x00000025 r1:0x00800D80=>0x00000025 [0x00800D83]=1317b025

```

Then I changed the address to a different and distinctive address, and then the new address showed up in the same places:

```

0x00000af8->0x00000afa Thumb Supervisor 0x00000af8 0x78c9 LDRB r1, [r1, #0x3] r1:0x00800DA0=>0x00000025 r1:0x00800DA0=>0x00000025 [0x00800DA3]=409f7025

```

The LDRB instruction only loads a single byte, but my tracer always reads 32 Bits (a DWord) from the memory location that is accessed. So we are accidentally finding the sector address here, and the CPU is only interested in a single byte next to it, which turned out to be the SATA request command byte.

So with trace sequencing, I found where the SATA PHY hands over the requested block address to the CPU:

0x00800DA0 seems to be one of the base addresses of an incoming SATA Request. 0x00800DA3 (base\_addr+3) contains a byte with the SATA request command. Some important SATA commands: 0x25 read DMA extended (LBA48) (LBA=Logical Block Address) 0x35 write DMA extended (LBA48) 0x92 Download microcode (Firmware Update) 0xb0 SMART

If you are more interested in the SATA commands: <u>http://www.t13.org/</u> <u>http://www.t13.org/documents/uploadeddocuments/docs2006/d1699r3f-ata8-acs.pdf</u>

Some of the base addresses I observed in the various sequences were

(strings debugmex\* |grep 0x00000af8 |grep -v LDRB |sort |uniq)

0x00800C00 0x00800C10 0x00800C40 0x00800C50 0x00800C90 0x00800CB0 0x00800DE0 0x00800DE0 0x00800DF0 0x00800E00

So everything from 0x00800C00-0x00800E0F is definitely SATA Requests (perhaps the range is even bigger) and the whole 0x00800XXX is potentially SATA PHY related, I would say. Another thing this tells us is that there are likely only 16 bytes for every SATA request available here.

Later on I discovered that there are actually 33 NCQ (Native-Command-Queuing) Buffers for the requests:

The first buffer starts at 0x00800C00, the second one at 00800C10, ... so 0x00800DA0 is actually the 26th request buffer, and the final buffer starts at 0x00800E00 and ends at 00800E1F. And every request buffer is 16 bytes long, and contains the SATA command, the requested address, ...

And even another thing is that the sector address does not actually seem to be read by mex1, so the whole memory management, wear-leveling, block relocation and tabling seems to be done by different cores.

All those addresses are definitely in the BTCM range (TCM=Tightly Coupled Memory, which is a fast SRAM that is tightly coupled to the CPU, most ARM chips have 2 TCM interfaces, named ATCM and BTCM) (ATCM starts at 0x0 and is 0x20000 large, BTCM starts at 0x80000 and is 0x28000 large)

So either the SATA PHY can write into the BTCM itself (or with some DMA help), or the SATA PHY is memory mapped over the BTCM.

Then I looked at what happens after the SATA command byte is read by mex1.

The interesting thing is that the command byte (256 different possibilities) is hashed (multiplied, cut-off, shifted around, multiplied, shifted again),

and then it is looked up in a 16 entry hash table. Unfortunately hash-tables have the unfortunate property of possibly having collisions, and shoveling 256 possibilities into a 16 entry hash table makes that a practical problem,

so they created linked lists (or perhaps even trees) for every hash-table entry where the right entry for a specific command byte is searched.

When the right entry is found, and the function address is not null, the command-handler function is called. If it is null, an error handler is called.

I would suggest to replace this complex construct with a simple 256-entry function pointer table, where every command byte that is not defined is redirecting directly to the error handler.

That way you would get constant O(1) performance, and likely about 1 microsecond less latency for every SSD request, which the current SSD firmware wastes in the hash-table lookup.

Some more thoughts about the trace sequencing:

Even after some days of sampling, I still had sequence ends where I never had a sample that would match to it.

In one case I had 3 different sequences that all ended in the same instruction, but none of the sequences had the following instruction in it.

So it seemed to me that there are barriers that I do not fully understand yet.

The first and easy reaction was to just do more sampling of sequences.

But after thinking about it for a few days, I thought that perhaps the code runs at different speeds (e.g. due to interacting with fast TCM RAM or with slow IO devices elsewhere. Or Cache Hits/Misses)

If I always randomly interrupt the code, it is more likely that I hit slow running code than hitting fast running code, which should result in more sequences covering slow running code and less sequences covering fast running code.

Since I am always capturing 90 instructions, when the first instruction is a slow instruction, I might usually only get the first 90 instructions after a slow instruction and only very seldom instructions beyond the 90 after a slow instruction will be reached.

The way to verify this assumption is to calculate the distribution of all all the first instructions of a sequence among all instructions traced.

If there are significant differences, then the speed differences are likely a problem. (To be done ...) But how can we mitigate this problem?

My current idea is identify dead-ends, and to specifically put breakpoints at those dead-ends, and to start tracing from where the break-point hits, instead of randomly halting the CPU and tracing from there.

When you succeeded to continue tracing at a dead end, then you will likely want to do the same again with the most likely newly found dead-end again. (To be done...)

So that's effectively a feedback-loop between sampling and sequencing.

The quest for the longest sequence.

So I developed my puzzle tool, which puzzles the sequences together.

I first started with the simple idea of taking the first sequence that was sampled, and at the end of the sequence, it looks through all occurrences of the needed next address.

It makes sure that the overlapping of a potential sequence with the sequence we need it for is good. If the sequences fit, it attaches them together, and continues again at the end.

When we can find no more sequences, we are done.

One problem I saw quite early was that the algorithm often fell into short loops. What I did then was to randomize the list of potential sequences to be attached to the current one, which solved this short loop problem.

Another change I want to do is to remove the possibility to reuse sequences that were used already, which should remove long loops.

### SHA256:

In the bad SSD, I found a SHA256 implementation in memory, in the blocks <u>0x80000000</u> and <u>0x80010000</u>.

At 0x20064 in P23 which gets mapped to <u>0x80020264</u> I found the SHA1 hash initialization values ddcc7 on Reddit found the same on a the firmware for the Samsung 840 (not EVO). <u>https://www.reddit.com/r/ReverseEngineering/comments/2uwhls/</u><u>samsung\_ssd\_firmware\_deobfuscation\_utility/</u>

On the HDDGURU forum, I got the hint that SHA256 is used together with an elliptic curves digital signature to protect the firmware updates. Later on, I found something that looked like HMAC-SHA256, but it does not seem to be used for the firmware-update, it seems to be used elsewhere (TCG-OPAL perhaps?).

### COMINIT/COMRESET

One question I researched is whether SATA PHYs usually automatically initiate/respond the COMINIT/COMRESET/COMWAKE signals, or whether the CPU has to signal to the SATA PHY that it should do that.

The SATA\_PHY project on OpenCores seems to require this signaling from the CPU: <u>http://opencores.org/websvn,filedetails?repname=sata\_phy&path=%2Fsata\_phy%2Ftrunk%2Fdoc</u> <u>%2FSATA+PHY+Design+Manual+v1\_0.pdf</u>

2 other cores I found

http://www.synopsys.com/IP/InterfaceIP/SATA/Pages/default.aspx http://ip.cadence.com/ipportfolio/ip-portfolio-overview/interface-ip/serdes-ip/sata-phy do not seem to require signaling and do the initial communication themselves. They only need a signal, whether they should behave as host or device, but this can be baked and optimized away, I guess.

In the end it turned out that COMINIT/COMRESET has to be signaled with the CPU, and mex1 cares about it: When I made the change from inserting the SSD into a USB drive bay (for easier handling) to connecting the SSD with separate power and data cables, I tried to see what happens when the SSD is only connected through power but does not get talked to through SATA data, and found that the SSD was able to cope with that:

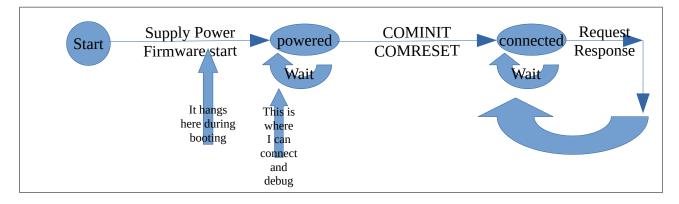

So we have a state-machine that looks approximately like this:

As soon as the SSD is connected with power, it starts the firmware, when the initialization is done, it starts waiting for a connection with the HOST computer (a small loop that checks the status register 0x200000AC bits for the COMINIT signal), when that signal is given, it continues by configuring the SATA PHY for the connection, and then it starts waiting for Requests from the computer.

The problem with my SSD is that the Firmware start seems to initialize the SATA PHY properly in the beginning, but it then somehow deviates from the correct program flow and does not get to the "powered wait" loop. If the firmware would get to the "powered wait" loop, it could get the COMINIT signal from the SATA PHY and could continue properly.

So where and why does it deviate? Where are possible branches in the program flow that could lead to where the bad SSD is at the moment?

Later on, I found out that the reason is a problem in the flash channels that is detected by the firmware, and therefore it stops starting and does not enable the SATA interface.

### **Reverse Engineering Platform**

To speed up reverse engineering, I started to develop a Crowd-Sourcing Reverse Engineering Platform:

http://www2.futureware.at/~philipp/ssd/analyse/EXT0CB6Q.dec.html

Memory:

| Readable    | memory   | regions:        |        | Contin       | uous Mer | nory Dun | ip Sect | tions: deta        | ailed Mem | ory Map  |                                                                         |

|-------------|----------|-----------------|--------|--------------|----------|----------|---------|--------------------|-----------|----------|-------------------------------------------------------------------------|

|             |          |                 |        | ID S         | tart     | Size     | Short   | Bytes              | Writeable | Readonly | Comments                                                                |

|             |          |                 |        | R1 0         | 0000000  | 00020000 | ) 2     | 128 KB             | 2         | 0        | ATCM, GOOD=BAD                                                          |

|             |          |                 |        | R2 0         | 0800000  | 0080000  | 128     | 8 MB               | 128       | 0        | BTCM, Contains Instructions (Bad-Cycle IP:=0x0081b810) [P11->0x816000]  |

|             |          |                 |        | R3 1         | 0010000  | 00020000 | ) 2     | 128 KB             | 2         | 0        | DMA, IPC                                                                |

|             |          |                 |        | R4 1         | 0040000  | 00020000 | ) 2     | 128 KB             | 0         | 2        | DEBUG ROM (CoreSight)                                                   |

|             |          |                 |        | R5 1         | 0100000  | 00100000 | ) 16    | 1 MB               | 0         | 16       | GOOD=BAD                                                                |

|             |          |                 |        | R6 2         | 0000000  | 00600000 | 96      | 6 MB               | 9         | 87       | PHYs (2028-202F, 2051-205F GOOD=BAD) Data: Read from 0x203B000C         |

|             |          |                 |        | R7 4         | 0000000  | 0300000  | 768     | 48 MB              | 768       | 0        | BTCM of MEX1 (starts with GOOD=BAD) [P21+P22+P31+P32+P41+P42]           |

|             |          |                 |        | R8 4         | 4000000  | 0300000  | 768     | 48 MB              | 768       | 0        | BTCM of MEX2 (starts with GOOD=BAD)                                     |

|             |          |                 |        | R9 4         | 8000000  | 0300000  | 768     | 48 MB              | 768       | 0        | BTCM of MEX2(starts with GOOD=BAD)                                      |

|             |          |                 |        | R10 <u>8</u> | 0000000  | 20000000 | 8192    | 512<br>MB          |           | 8191     | RAM - [P23+P33+P43] - Samsung 512 MB LP-DDR2 SDRAM, but mostly readonly |

| Firmware    | Sections | :               |        |              |          |          |         | CPU Co             | res:      |          |                                                                         |

| Partition   | Start    | Map             | Size   | Size         | good     | good2    | bad     | mex1 R             | WX        |          |                                                                         |

| Phead       | 0        | N/A             | 512    | 0,5K         | в        |          |         | mex <sub>2</sub> R | WX        |          |                                                                         |

| P11         | 512      | <u>0x816000</u> | 81408  | 79 K         | B 47694  | 47696    | 41602   | mex3 R             | WX        |          |                                                                         |

| P21         | 81920    | 0x40000000      | 131072 | 128 K        | B 4      | 4        | 4       |                    |           |          |                                                                         |

| <b>P</b> 22 | 212002   | 0x40808000      | 32768  | 32 K         | B 224    | 224      | 0       | Trace Lo           | gs        |          |                                                                         |

12992 0x40808000 32768 32 KB SATA Command Table 121 Memory Map <u>P23</u> 245760 0x80000200 196608 192 KB 133055 133055

245760 0x80000200 190008 192 KB 19900 200 192 KB 199000 200 192 KB 19900 2 P31

The first page is the memory view. In the upper left area you see an image of the 4GB memory space of the ARM cores. Every pixel represents a 64KB block of the memory. The dark-gray areas are accessible memory, the light-gray areas are unallocated address-space. The red area is the one you have currently selected.

On the right side of it you see a table with all the contiguous memory regions that I have identified so far. When you move your mouse over the table, you will see the specific region highlighted in red on the left image. When you click on the start address a new window/tab will open with a memory browser. If you can identify anything interesting, please leave a comment by clicking on "Comment" and fill the form there.

In the lower left area you can see the firmware that was provided by Samsung on their website, and the sections, and where they are mapped to. When you click on the links in the partition number field, you get to a memory comparison between the bad SSD, and 2 different readouts of the good reference SSD. (If the 2 different readouts of the good SSD are different, that means that it is volatile and differences between the good and the bad SSD are likely not a problem).

On the lower right side you have a table of the 3 ARM cores and their read- write- and execute behavior. When you move your mouse over the cells, you can see the traces of the behavior on the image in the upper left area.

Below that, you have a link to the Debug Traces that I collected: <u>http://www2.futureware.at/cgi-bin/ssd/logs</u>

|                  | CPUs                                                                                                                                                   | CPUs                     |                                                 |                         |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------|-------------------------|--|--|--|

|                  | mex1                                                                                                                                                   | mex2                     | mex3                                            | mex?                    |  |  |  |

| 952085           | mex1952085                                                                                                                                             |                          |                                                 |                         |  |  |  |

| ?                |                                                                                                                                                        |                          |                                                 | good 2 MB good<br>30 MB |  |  |  |

| analyse          | mex1analyse 1 MB                                                                                                                                       |                          |                                                 |                         |  |  |  |

| bad              | mex1-bad-idle                                                                                                                                          |                          |                                                 |                         |  |  |  |

| boottry          | mex1-boottry                                                                                                                                           |                          |                                                 |                         |  |  |  |

| cutout1192835    |                                                                                                                                                        | mex2cutout1192835        |                                                 |                         |  |  |  |

| devslp242845     | mex1devslp242845                                                                                                                                       |                          |                                                 |                         |  |  |  |

| devslp693816     |                                                                                                                                                        | mex2devslp693816         |                                                 |                         |  |  |  |

| encryption187565 | mex1encryption187565 8 MB                                                                                                                              |                          |                                                 |                         |  |  |  |

| identifydevice   | mex1-identifydevice-good 2 MB                                                                                                                          |                          |                                                 |                         |  |  |  |

| idle             | mex1-idle 4 MB                                                                                                                                         | mex2-idle 3 MB           |                                                 |                         |  |  |  |

| init             | mex1-init-bad 1 MB mex1-init-good-3 mex1-init-good-4 mex1-init-good-5 mex1-init-good-loop mex1_init mex1init-2 mex1init-<br>goodcontinue 1 MB mex1init |                          |                                                 |                         |  |  |  |

| initnodata       | mex1-initnodata                                                                                                                                        |                          |                                                 |                         |  |  |  |

| loggg            | mex1loggg                                                                                                                                              |                          |                                                 |                         |  |  |  |

| op1              | mex1op1                                                                                                                                                |                          |                                                 |                         |  |  |  |

| queryseq         | mex1queryseq 144 MB                                                                                                                                    | mex2queryseq 140 MB      |                                                 |                         |  |  |  |

| ramwait          |                                                                                                                                                        | <u>mex2-ramwait-a</u>    | mex3ramwait-3 3 MB mex3ramwait-d<br>mex3ramwait |                         |  |  |  |

| ramwaitcontinue  |                                                                                                                                                        |                          | mex3ramwaitcontinue-2<br>mex3ramwaitcontinue    |                         |  |  |  |

| read             | mex1read-2 mex1read-3 mex1read 4 MB                                                                                                                    | mex2read 30 MB           | mex3read 4 MB                                   |                         |  |  |  |

| read1317b7       | mex1read1317b7 1 MB                                                                                                                                    |                          |                                                 |                         |  |  |  |

| read409F75       | mex1read409F75                                                                                                                                         |                          |                                                 |                         |  |  |  |

| readComplete     | mex1_readComplete_1020 KB                                                                                                                              |                          |                                                 |                         |  |  |  |

| readcomplete     | mex1readcomplete 13 MB                                                                                                                                 | mex2readcomplete 1 MB    | mex3readcomplete 1 MB                           |                         |  |  |  |

| readincomplete   |                                                                                                                                                        | mex2_readincomplete 7 MB |                                                 |                         |  |  |  |

| safe             | mex1-safe-good-read_mex1-safe-press-r-UART_REGISTER_mex1-safe-pressunknown 3 MB_mex1-safe-pressunknown2<br>mex1safe-press-enter                        |                          |                                                 |                         |  |  |  |

| safereadblock    | mex1safereadblock-12345 mex1safereadblock-2 mex1safereadblock                                                                                          | î                        | î                                               | -i                      |  |  |  |

I sorted them by CPU core and by the workload that was executed during the trace.

Then I added search functions: When you click on the link on "x" on the addresses, it searches through all traces for all executions of this instruction, so that you can compare the different data that flew through this instruction, and see under which workloads the code is needed.

I have published the software behind this platform on GitHub: <u>https://github.com/thesourcerer8/CrowdRE</u>

If you have any improvement ideas for the platform, please post issues on GitHub.

Regarding discussing and organisation, started a discussion thread on the Kosagi Forum for Novena Firmware: <u>https://www.kosagi.com/forums/viewtopic.php?id=421</u>

To discuss the hardware and electrical side of the SSD, I started a thread on the HDDGURU forum: <u>http://forum.hddguru.com/viewtopic.php?f=13&t=34306</u>

I still have a lot of things that I started on that I haven't fully finished visualising yet.

For example, I measured the entropy of the blocks (bad,good,good2) and whether they are identical or different:

http://www2.futureware.at/~philipp/ssd/todo/changes.txt

I collected all read, write and execute accesses of the traces and compiled them in a list: <u>http://www2.futureware.at/~philipp/ssd/loganalyse.txt</u>

One analysis I want to make is for read/write access to the same address by different cores, which could identify Inter-Core Communication.

### **Disassembling & Decompiling**

After a lot of tracing, I reached some limitations of tracing:

Some code areas are hard to reach, similar to reaching 100% test coverage in testing. Especially if you do not know the sourcecode and it's intentions.

So I started to investigate the disassembling and decompiling again.

As targets I chose Radare2 and IDA Pro.

In my first experiments, I wanted to mount all the sections from the complete 4GB memory space into radare, so that radare can see all data and interpret it correctly. But then I decided to start with the firmware code that is used for initialisation of mex1, which located in the 128KB right at the beginning.

First I took all the comments, and filtered the Safe-mode comments away.

Radare gets "CC comment" @address and IDA Pro gets MakeComm()

I took all the trace logs, filtered them for the mex1 instructions in normal mode (not Safe mode), and generated ahb commands for radare2 and SetRegEx() for IDA Pro for every instruction to signal ARM/THUMB mode.

Then I searched for BL/BLX instructions in the trace logs, which are function calls. Even call addresses jump to ARM code, uneven addresses are signaling THUMB code, and have to be decremented for the real target address. For every function call, I generate SetRegEx(), MakeFunction() and MakeName() for IDA Pro and ahb, f and af for Radare.

If you want to use radare2 or IDA Pro yourself, take a look here: <u>http://www2.futureware.at/~philipp/ssd/disasm.html</u>

Later on, I gave tracing another try, and figured out how to configure Linux not to timeout on SATA requests. The following command raises the timeout for 1 million seconds, which was enough to trace the full behavior for the disk "sda" (you have to replace sda with the devicename of the SSD on your system)

```

echo 1000000 >/sys/block/sda/device/timeout

```

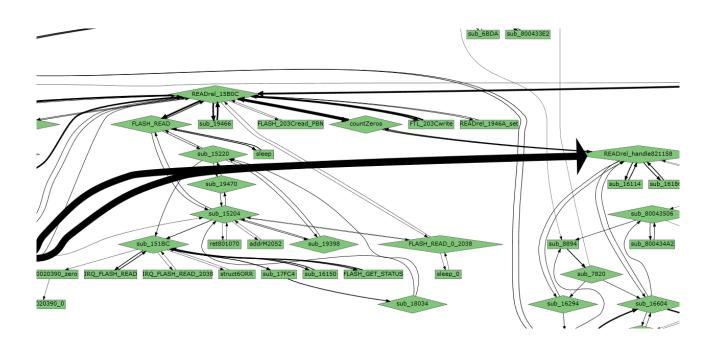

## **Firmware Flow visualsation**

I used a commercial tool PQM for business process analysis to visualize the flows that I traced between the various functions, this helped a lot to understand what is actually going on in the firmware. The following screenshot shows read requests that are handled on mex2:

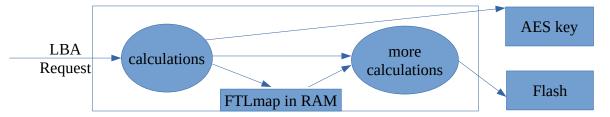

### Flash Translation Layer (FTL)

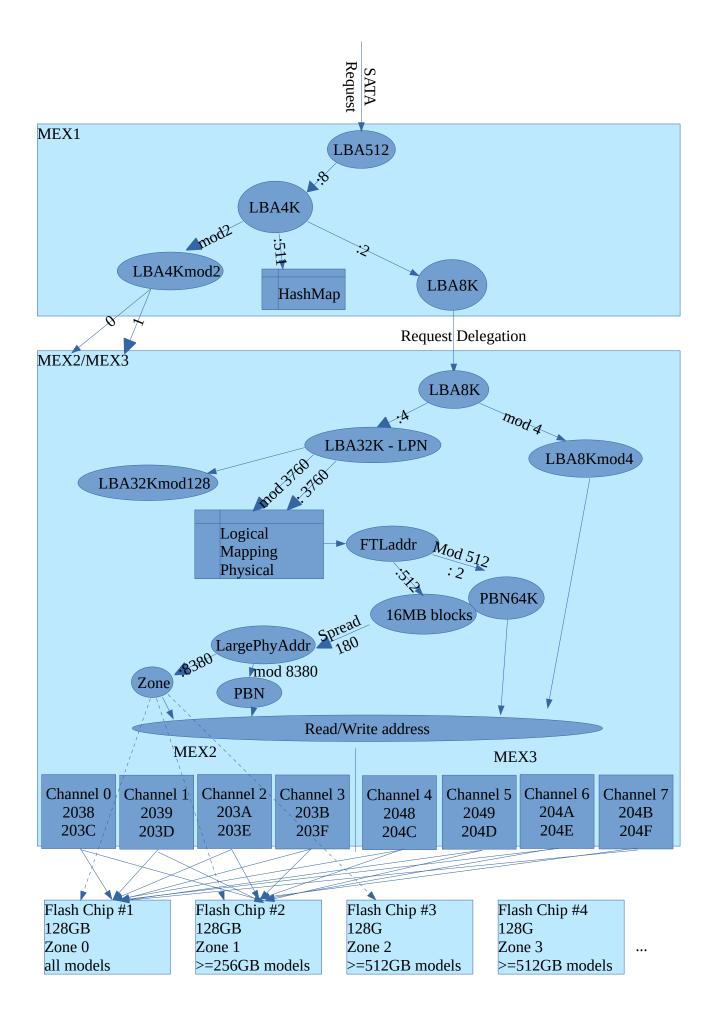

The Flash Translation layer is spread across the 3 cores in the following way:

At first, MEX1 (likely named HCORE or Host-Core by Samsung) receives the SATA requests, as LBA512 addresses (LBA addresses for 512 Byte-Blocks. LBA stands for "Logical-Block-Addressing" which). It divides the LBA512 down to LBA4K and LBA8K addresses. 8K (and larger) requests are split up into 4K requests.

The LBA4K addresses modulo 511 are looked up in HashMap with a Linked list that is empty when starting and is getting filled primarily with Write requests, but sometimes also Read requests end up there.

The LBA4K address modulo 2 (also known as the LSB) is used to decide, whether the request is delegated to MEX2 or MEX3 (they are likely named F-Cores, or Flash-Cores by Samsung).

Then the request is delegated to MEX2 or MEX3, and only the LBA8K address is handed over with the delegation, together with a bitmask which signals which 512-byte-parts of the 8K block are actually to be read.

Now from the MEX2/MEX3 perspective:

MEX2/MEX3 receive the delegated command with the LBA8K address, and divides it by 4 to calculate the LBA32K address. (MEX2 intrinsically knows that is always responsible for the lower 4KB and MEX3 knows that it is responsible for the upper 4KB of the 8K request they get)

The LBA32K modulo 128 is used to lookup something at 0x823168.

Then the LBA32K is further divided and modulo'd by 3760, into LBA32div3760 and LBA32mod3760, which are first used to lookup in a bitfield, and later on in a Hashmap for the FTLaddr (Flash-Translation-Layer-Address), this is the core of the mapping from the LBA32K address to where it is stored in the Flash.

At first I thought that the LBA32K address is mapped to the FTLaddr, which would make it 32Kaligned/sized. But later on, I realized that the FTLaddr is actually 4KB aligned/sized. It turned out that there are 8 tables (4 tables are used by MEX2, the other 4 tables by MEX3) which translate from LBA8K  $\rightarrow$  FTLaddr, and the FTLaddr is different for different 8KB-blocks inside the same 32KB block, so the FLTaddr is actually 4KB sized. And those 8 tables actually correspond to the 8 flash channels.

Now the situation gets a bit difficult, because the flash is organized in several dimensions (Zone, Channel, PBPN, FTLbit), and depending on the order in which you look at those dimensions, the sizes are very different. (The plan to figure out which dimension means what is to try Erasing and seeing which dimensions are affected and which are not affected)

The FTLaddr is then devided by 512 to get a 16-MB size, the rest is remembered as PBN64K as 32K offset into the 16MB blocks. The 16MB could be the Erase-Size.

Now this 16MB is spread by180 16MB blocks, which is about 2.8 GB of space for the SA area at the beginning of every physical Flash chip on the PCB. This results in the "LPA, the LargePhysicalAddress". The LPA is then divided by 8380, which is the Zone (which physical chip on the PCB), and the rest is the PBN (Physical Block Number), which is the physical 16MB Block inside the Physical Chip.

To read/write the physical chip, the PBN64K is added again to the 16MB-sized PBN (Physical Block Number) and together they form the PBPN (PhysicalBlockandPageNumber).

So with the Zone you address the physical chip, with the PBPN you address the 8KB page inside the chip, and with the bitfield you select which of the 512 Blocks in the 8KB block you want to read.

So I was missing the last 3 bits between the 8KB and 64KB. I guessed that they might be given by 8 Flash controllers. It first turned out that all 8 flash controllers have access to the same data, but I later found out that this must been a special case, and those 3 bits are actually into which flash channel to use.

On the other hand, we have 2 chips which are together 250 GB, so one of them must hold a little more than 125 GB. Since the LPA is divided by 8380, we would get 134080 MB / 8380 = 16 MB, so a PBN should be 16MB in size, not 8KB. If we would take 8KB\*256\*83800\*2, we would get only 16 GB capacity per chip. That's what I meant with the dimensions ...

### TRIM SUPPORT